# 2023 年春季学期

# 数字电子技术基础 期末复习检测

2023.6 V1.2

说明:测试时间 120 分钟,满分 100 分。可以使用无编程、记忆功能的计算器。

# 注意行为规范 遵守考场纪律 祝大家取得好成绩!

### 一、填空(共10个小题,满分27分)

| · ************************************ | 10 1 1 /25 1/4/3 | =1 /4 / |                   |                     |     |

|----------------------------------------|------------------|---------|-------------------|---------------------|-----|

| 1.(2分)将(107.39)10转换为等值二进制数             |                  |         | (保留小数点后 4 位有效数字), |                     |     |

| 转为 8421-BCD                            | 码表示              | 0       |                   |                     |     |

| 2.(2分)以高、                              | . 低电平表示两种不       | 同逻辑状态时的 | 的两种定义方法分别         | 为、                  | o   |

| 3. (3分)在下                              | 列门电路中,           | 能实现"线与  | "逻辑功能;            | 能用于总线结              | 构的数 |

| 据传输;                                   | 能实现模拟信号的         | 双向传输。(填 | 编号)               |                     |     |

| A.异或门;                                 | B.OC 门;          | C.三态门;  | D.传输门。            |                     |     |

| 4. (2分) 写出图                            | 图 1 中逻辑图的逻辑      | 函数式: Y= | (无需化简)。           |                     |     |

| A I B                                  | =                | Ĭ       |                   | G <sub>2</sub><br>→ |     |

图 2

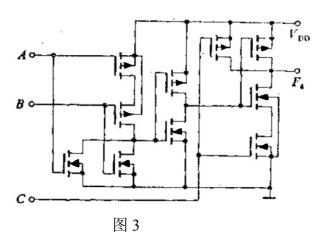

6. (3分)如图 3, $F_4$ 关于 A、B、C 的逻辑表达式为\_\_\_\_\_(无需化简)。

图 1

7. (3 分)某 TTL 反相器的输入短路电流  $I_{S=1.4mA}$ ,高电平输入漏电流  $I_{R}=0.02mA$ ,最大低电平输出电流  $I_{OL(max)}=15mA$ ,最大高电平输出电流  $I_{OH(max)}=0.4mA$ ,则其扇出系数  $N_0=$ \_\_\_\_。8. (3 分)用与非门构成的 SR 锁存器的约束条件为

9. (2分) 双积分型 A/D 转换器属于\_\_\_\_\_(直接型/间接型) A/D 转换器。

10. (3分)4位扭环型计数器的计数长度为。

#### 二、(8分)

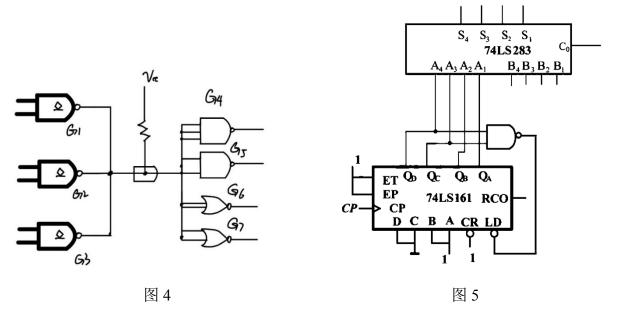

计算图 4 所示电路上拉电阻的取值范围。其中 G1、G2、G3 是 74LS 系列 OC 门,输出管截止时的漏电流  $I_{OH} \leq 100 \mu A$ ,输出低电平  $V_{OL} \leq 0.4 V$  时允许的最大负载电流  $I_{OL\ (max)} = 8mA$ 。 G4~G7 为 74LS 系列门电路,它们的输入电流为  $I_{IL(max)} = -0.4 mA$ , $I_{IH(max)} = 20 \mu A$ 。给定  $V_{CC} = 5 V$ ,要求 OC 门的输出高、低电平应满足  $V_{OH} \geq 3.2 V$ 、 $V_{OL} \leq 0.4 V$ 。

## 三、(10分)

如图 5 所示电路由同步十六进制计数器 74LS161、四位加法器 74LS283 和与非门组成, $C_0$ 为来自低位的进位信号,回答下面问题:

- 1. 74LS161 和与非门构成多少进制计数器?

- 2. 按着 Q<sub>D</sub>Q<sub>C</sub>Q<sub>B</sub>Q<sub>A</sub> 的顺序, 74LS161 的输出是什么编码?

- 3. 若要求从 S<sub>4</sub>S<sub>3</sub>S<sub>2</sub>S<sub>1</sub> 输出为 BCD8421 码,则 B<sub>4</sub>B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>及 C<sub>0</sub>应如何连接?

# 四、(10分)

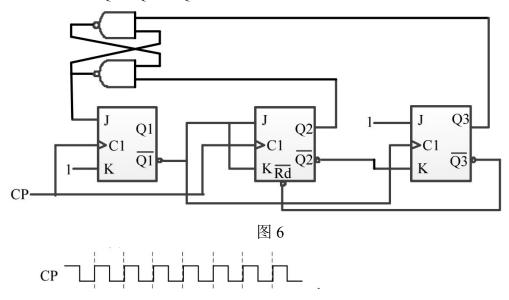

由 JK 触发器和 SR 锁存器组成的电路如图 6 所示,各触发器初始状态为 0,画出 7 个时钟 CP 作用下 Q3, Q2 和 Q1 的时序图。

## 五、(12分)

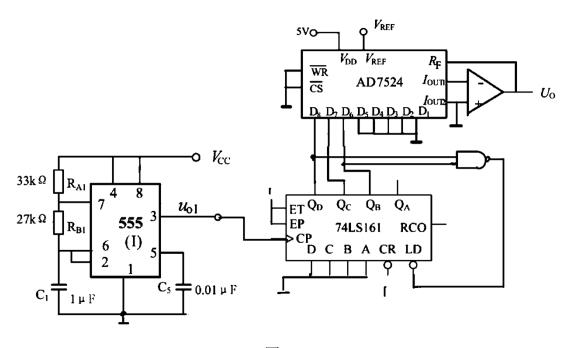

图 7 中 AD7524 为 8 位倒 T 形电阻网络 D/A 转换器,当  $D_6$ =1,其余各位为 0 时, $U_0$ =一  $1V_0$ 74LS161 为同步十六进制加法计数器,其中  $Q_D$ 为最高位。时钟 CP 由 555 定时器输出引入。  $1.求 \mid U_0 \mid$ 的最大值;

#### 2.求 Uo的频率。

图 7

## 六、(7分)

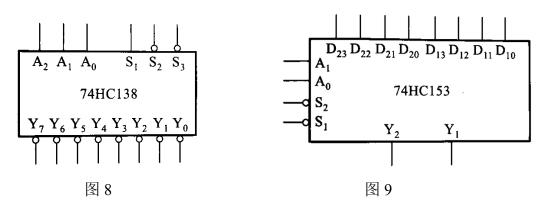

已知逻辑函数  $F(A, B, C, D)=\Sigma m$  (0, 2, 3, 4, 5, 6, 7, 11, 12)+  $\Sigma d$  (8, 9, 10, 13, 15),用两片 74HC138 和最少的二输入与门实现 F。74HC138 的元件符号如图 8。

### 七、(12分)

设计一个序列"010100"发生器。该序列由一个输入数字量 X 控制,当 X=0 输出该序列,当 X=1 时固定输出 1。使用 JK 触发器、一片双 4 选 1 数据选择器 74HC153 和尽可能少的门电路实现。74HC153 的元件符号如图 9。

### 八、(14分)

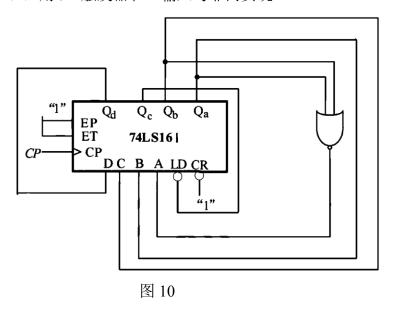

由中规模十六进制加法计数器 74LS161 构成的电路如图 10 所示。

- 1. 给出 74LS161 的输出[ $Q_D Q_C Q_B Q_A$ ]的完整状态转换图,并说明构成几进制计数器;

- 2. 用边沿触发的触发器实现该电路功能。给出驱动方程即可,不必画出电路图。要求:

- (1) 用 D 触发器和必要的门电路实现。

- (2) 用 JK 触发器和二输入与非门实现。

附加题(15分)建议限定的时间到后,额外抽出一点时间做做这个题,很综合很全面。

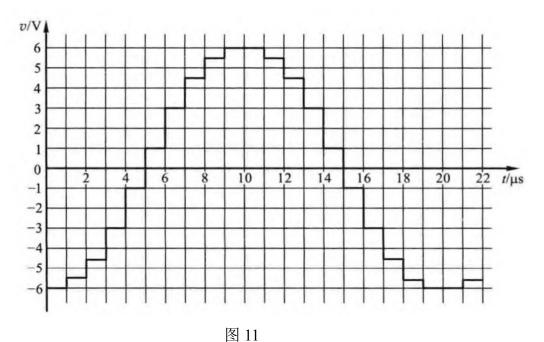

设计一个波形发生器电路,要求产生如图 11 所示的电压波形。